Департамент образования, науки и молодёжной политики Воронежской области

Государственное бюджетное профессиональное образовательное учреждение Воронежской области

«Воронежский государственный профессионально-педагогический колледж»

Цикловая методическая комиссия профессионального цикла специальности Компьютерные системы и комплексы, математических и естественнонаучных дисциплин

Е.А. Данилова

# МЕТОДИЧЕСКИЕ РЕКОМЕНДАЦИИ

для лабораторных работ

МДК.06.01

Цифровая схемотехника

Воронеж

2017

УДК 808 ББК 74.26 Б 18

#### Рецензент:

преподаватель высшей квалификационной категории, председатель цикловой методической комиссии профессионального цикла специальности Компьютерные системы и комплексы, математических и естественнонаучных дисциплин ГБПОУ ВО «ВГППК» Е.А. Савченко.

Методические указания для лабораторных работ по МДК.06.01 Цифровая схемотехника / Е.А. Данилова. — Воронеж: ВГППК, 2017. — 42 с. Методическое пособие предназначено для обучающихся по специальности 44.02.06 Профессиональное обучение (по отраслям), специальность профиля подготовки 09.02.01 Компьютерные системы и комплексы, как руководство для организации лабораторных работ по МДК.06.01 Цифровая схемотехника, которое может быть использовано в учебном процессе колледжа.

Печатается по решению совета учебно-методического центра ГБПОУ ВО «Воронежский государственный профессионально-педагогический колледж»

© ГБПОУ ВО «Воронежский государственный профессионально-педагогический колледж», 2017

# Оглавление

| ВВЕДЕНИЕ                                                                       | 4  |

|--------------------------------------------------------------------------------|----|

| ЛАБОРАТОРНАЯ РАБОТА №1                                                         | 6  |

| Тема: знакомство с программой Workbench.                                       | 6  |

| ЛАБОРАТОРНАЯ РАБОТА №2                                                         | 12 |

| Тема: исследование логических элементов и синтез схем.                         | 12 |

| ЛАБОРАТОРНАЯ РАБОТА №3                                                         | 16 |

| Тема: исследование шифраторов и дешифраторов.                                  | 16 |

| ЛАБОРАТОРНАЯ РАБОТА №4                                                         | 19 |

| Тем: исследование мультиплексоров и сумматоров.                                | 19 |

| ЛАБОРАТОРНАЯ РАБОТА №5                                                         | 24 |

| Тема: исследование цифровых компараторов и устройств чётности.                 | 24 |

| ЛАБОРАТОРНАЯ РАБОТА №6                                                         | 27 |

| Тема: исследование триггеров.                                                  | 27 |

| ЛАБОРАТОРНАЯ РАБОТА №7                                                         | 21 |

| Тема: исследование счётчиков.                                                  | 21 |

| ЛАБОРАТОРНАЯ РАБОТА №8                                                         | 24 |

| Тема: исследование регистров.                                                  | 24 |

| ЛАБОРАТОРНАЯ РАБОТА №9                                                         | 28 |

| Тема: арифметико-логическое устройство.                                        | 28 |

| ЛАБОРАТОРНАЯ РАБОТА №10                                                        | 30 |

| Тема: оперативные запоминающие устройства, постоянные запоминающие устройства. | 30 |

| СПИСОК ЛИТЕРАТУРЫ                                                              | 33 |

### Введение

Курс «Цифровая схемотехника» направлен на изучение теоретических предоставление практических основ навыков проектирования использования цифровых электронных схем и цифровых устройств. Структура курса состоит из изучения теоретических основ элементов и узлов цифровой схемотехники. Рассматриваются комбинационные и последовательные схемы, память проектирование цифровых устройств на программируемых логических интегральных схемах. Кроме того, изучаются аналогово-цифровые и цифро-аналоговые и преобразователи, аналоговые и цифровые таймеры, а также генераторы цифровых последовательностей и вопросы тестирования цифровых схем.

Лабораторные работы предназначены для закрепления теоретических знаний студентов, получения навыков практического применения цифровых электронных схем и умения использовать современную измерительную аппаратуру для исследования работы цифровых схем.

В методическом пособие изложена методика выполнения лабораторных работ, целью которых является знакомство с принципами работы основных узлов цифровой техники и выработка практических навыков инженерного проектирования и наладки устройств на микросхемах малой и средней интеграции. Методика рассчитана на компьютерное моделирование.

Workbench представляет собой программный продукт, позволяющий производить моделирование, тестирование, разработку и отладку электрических цепей, содержащих различные компоненты, в том числе и логические устройства. С помощью пакета можно проектировать различные цифровые устройства, такие как дешифраторы и шифраторы, сумматоры, триггеры, счетчики, регистры. Пакет допускает одновременное использование как аналоговых, так и цифровых устройств и позволяет проводить их совместное моделирование и тестирование.

Эффективность использования пакета Workbench определяется:

- интерфейсом пользователя;

- большим количеством моделей радиоэлектронных устройств;

- возможностью создавать свои модели;

- разнообразием видов анализа радиоэлектронных устройств.

Тема: знакомство с программой Workbench.

Цель: знакомство с работой программы Electronics Workbench.

Задание 1. Ознакомиться с основными компонентами программы

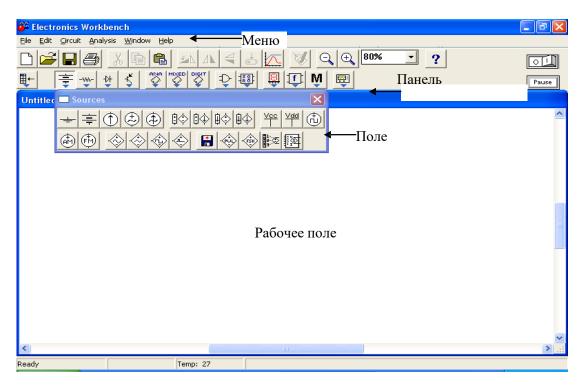

Для операций с компонентами на общем поле Electronics Workbench выделены две области: панель компонентов и поле компонентов (рис. 1. 1).

Puc 1.1 Окно программы Electronics Workbench

Панель компонентов состоит из пиктограмм полей компонентов, поле компонентов -из условных изображений компонентов. Щелчком мышью на одной из одиннадцати пиктограмм полей компонентов, расположенных на панели, можно открыть соответствующее поле. На рис. 1. 1 открыто поле источников (Sources). Расположение компонентов элементов полях Для ориентировано частоту использования компонента. описания на компонентов более логичным является разделение их по типам, чему мы будем следовать в дальнейшем, давая в каждом случае ссылку на поле, в

котором расположен компонент. При работе может быть открыто только одно поле компонентов. Перейдем теперь к описанию имеющихся в программе компонентов. В библиотеки элементов программы Electronics Workbench входят аналоговые, цифровые и цифро-аналоговые компоненты. Все компоненты можно условно разбить на следующие группы: • базовые компоненты, • источники, • линейные компоненты, • ключи, • нелинейные компоненты, • индикаторы, • логические компоненты, • узлы комбинационного типа, • узлы последовательного типа, • гибридные компоненты

### Источники (Sources):

заземление

Компонент «заземление» имеет нулевое напряжение и таким образом обеспечивает исходную точку для отсчета потенциалов. Не все схемы нуждаются в заземлении для моделирования. Однако, любая схема, содержащая: • операционный усилитель, • трансформатор, • управляемый источник, • осциллограф, должна быть обязательно заземлена, иначе приборы не будут производить измерения или их показания окажутся неправильными.

генератор тактовых импульсов

Генератор вырабатывает последовательность прямоугольных импульсов. Можно регулировать амплитуду импульсов, коэффициент заполнения (скважность) и частоту следования импульсов. Отсчет амплитуды импульсов генератора производится от вывода, противоположного выводу "+".

## Базовые компоненты (Basic):

соединяющий узел

Узел применяется проводников ДЛЯ соединения И создания контрольных точек. К каждому узлу может подсоединяться не более четырех собрана, проводников. После τογο, как схема онжом вставить дополнительные узлы для подключения приборов.

источник сигнала «логическая единица»

При помощи этого источника устанавливают уровень логической единицы в узле схемы.

ключ, управляемый клавишей (клавиша задается в **Key**)

# Индикаторы (Indicators):

пробник логического уровня

Пробник определяет логический уровень (0 или 1) в конкретной точке схемы. Если исследуемая точка имеет уровень логической 1, индикатор загорается красным цветом. Уровень логического нуля свечением не отмечается. На вкладке Choose Prob в меню Component Properties можно изменить цвет свечения пробника.

# Логические элементы (Logic Gates):

логическое НЕ

Элемент логическое НЕ или инвертор изменяет состояние входного сигнала на противоположное. Уровень логической 1 появляется на его выходе, когда на входе не 1, и наоборот.

Таблица 1.1 Таблица истинности:

| Вход А | Выход Ү |

|--------|---------|

| 0      | 1       |

| 1      | 0       |

логическое И

Элемент И реализует функцию логического умножения. Уровень логической 1 на его выходе появляется в случае, когда на один и на другой вход подается уровень логической единицы.

Таблица 1.2 Таблица истинности:

| Вход А | Вход В | Выход Ү |

|--------|--------|---------|

| 0      | 0      | 0       |

| 0      | 1      | 0       |

| 1      | 0      | 0       |

| 1      | 1      | 1       |

#### логическое ИЛИ

Элемент ИЛИ реализует функцию логического сложения. Уровень логической 1 на его выходе появляется в случае, когда на один или на другой вход подается уровень логической единицы.

Таблица 1.3 Таблица истинности:

| Вход А | Вход В | Выход Ү |

|--------|--------|---------|

| 0      | 0      | 0       |

| 0      | 1      | 1       |

| 1      | 0      | 1       |

| 1      | 1      | 1       |

# исключающее ИЛИ

Двоичное число на выходе элемента исключающее ИЛИ является младшим разрядом суммы двоичных чисел на его входах.

Таблица 1.4 Таблица истинности:

| Вход А | Вход В | Выход Ү |

|--------|--------|---------|

| 0      | 0      | 0       |

| 0      | 1      | 1       |

| 1      | 0      | 1       |

| 1      | 1      | 0       |

#### элемент И-НЕ

Элемент И-НЕ реализует функцию логического умножения с

последующей инверсией результата. Он представляется моделью из последовательно включенных элементов И и НЕ. Таблица истинности элемента получается из таблицы истинности элемента И путем инверсии результата.

Таблица 1.5 Таблица истинности:

| Вхол А | Вход В | Выход Ү |

|--------|--------|---------|

| 0      | 0      | 1       |

| 0      | 1      | 1       |

| 1      | 0      | 1       |

| 1      | 1      | 0       |

#### элемент ИЛИ-НЕ

функцию Элемент ИЛИ-НЕ реализует логического сложения c последующей инверсией результата. представляется Он моделью последовательно включенных элементов ИЛИ и НЕ. Его таблица истинности таблицы ИЛИ путем получается истинности элемента инверсии ИЗ результата.

Таблица 1.6 Таблица истинности:

| Вхол А | Вхол В | Выхол Ү |

|--------|--------|---------|

| 0      | 0      | 1       |

| 0      | 1      | 0       |

| 1      | 0      | 0       |

| 1      | 1      | 0       |

# исключающее ИЛИ-НЕ

Данный элемент реализует функцию "исключающее ИЛИ" с последующей инверсией результата. Он представляется моделью из двух последовательно соединенных элементов: исключающее ИЛИ и НЕ.

Таблица 1.7 Таблица истинности:

| Вход А | Вход В | Выход Ү |

|--------|--------|---------|

| 0      | 0      | 1       |

| 0      | 1      | 0       |

| 1      | 0      | 0       |

| 1      | 1      | 1       |

# Инструменты (Instruments):

логический преобразователь

Служит для исследования логических схем, можно производить анализ логических схем: строить таблицы истинности и получать логические выражения. С его помощью можно также производить синтез логических схем, т.е. по таблице истинности получить логическое выражения, а затем схему.

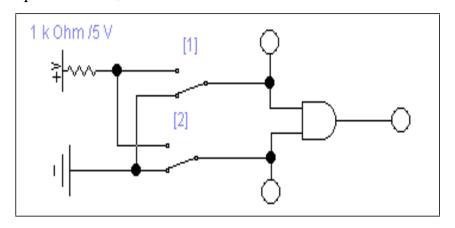

**Задание 2.** Составить схему (рис. 1.2). В последующих схемах заменить элементы и проверить таблицы истинности.

Рис. 1.2. Схема подключения элемента

Тема: исследование логических элементов и синтез схем.

Цель: исследование логических элементов с помощью программы Workbench, научиться синтезировать логические схемы.

**Задание 1.** Исследование логического элемента Исключающего ИЛИ с помощью аналитического анализатора.

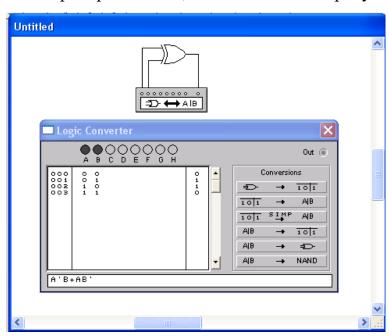

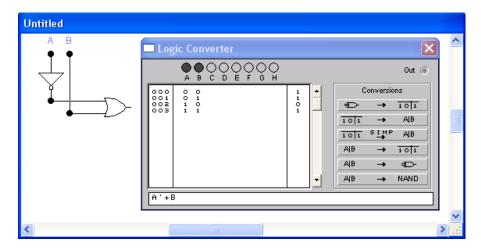

1. Собрать схему, состоящую из логического элемента Исключающее ИЛИ и аналитического преобразователя, как показано на рисунке 2.1.

Рис. 2.1 Вид рабочего поля

- 2. Двойным щелчком по схеме анализатора открыть диалоговое окно

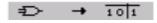

- 3. Сгенерировать таблицу истинности, щелкнув по кнопке

Это выражение приводится на дополнительном дисплее, расположенном в нижней части лицевой панели, в виде двух слагаемых, соответствующих выходному сигналу ИСТИНА (сигнал логической единицы на выходе OUT). Сопоставление полученного выражения с таблицей истинности убеждает нас

в том, что таких комбинаций действительно две, если учесть, что в полученном выражении приняты следующие обозначения: A'=0 — инверсия A=1, B'=0 — инверсия B=1, знак + соответствует логической операции ИЛИ.

**Задание 2.** Выполнить анализ следующих логических элементов: И, ИЛИ, ИЛИ-НЕ, И-НЕ, Исключающее ИЛИ-НЕ

#### Задание 3. Синтез логических схем

С помощью логического преобразователя можно проводить не только анализ логических устройств, но и их синтез. Допустим, что нам требуется составить схему и булево выражение для логического элемента, у которого выходная комбинация в таблице истинности не такая, как на рис. 2.1, а 1101. Для внесения необходимых изменений отмечаем курсором в столбце ОUТ подлежащий изменению символ, изменяем его с помощью клавиатуры и затем, перемещаясь по столбцу клавишами управления курсором, изменяем по необходимости символы в других строках. После внесения всех изменений последовательно нажимаем на клавиши

AlB → ⊅⊃-

Синтезированное логическое устройство показано в верхнем левом углу рис. 2.2, а его булево выражение — на дополнительном дисплее.

В более общем случае для выполнения синтеза целесообразно действовать следующим образом. Щелчком курсора по иконке логического преобразователя непосредственно на линейке приборов раскрываем его лицевую панель. Активизируем курсором клеммы-кнопки А, В...Н (начиная с А), количество которых равно количеству входов синтезируемого устройства. Вносим необходимые изменения в столбец ОUТ и после нажатия на панели преобразователя указанных выше клавиш управления получаем результат в виде схемы на рабочем поле программы и булево выражение в дополнительном дисплее.

Рис. 2.2. Рабочее поле после синтеза схемы

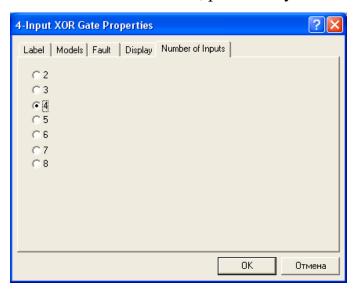

В заключение заметим, что для двухвходовых элементов можно увеличить количество входов до восьми, открывая двойным щелчком по значку компонента диалоговое окно (рис. 2.3). По умолчанию в этом окне указано минимально возможное число входов, равное двум.

Рис. 2.3 Диалоговое окно для изменения количества входов.

Задание 4. Выполнить синтез схемы, имеющей таблицу истинности:

Таблица 2.1. Таблица истинности:

| Вход А | Вход В | Вход С | Вход D | Выход Ү |

|--------|--------|--------|--------|---------|

| 0      | 0      | 0      | 1      | 0       |

| 0      | 0      | 1      | 0      | 1       |

| 0      | 0      | 1      | 1      | 0       |

| 0      | 1      | 0      | 0      | 1       |

| 0      | 1      | 0      | 1      | 1       |

| 0      | 1      | 1      | 0      | 0       |

| 0      | 1      | 1      | 1      | 0       |

| 1      | 0      | 0      | 0      | 1       |

| 1      | 0      | 0      | 1      | 1       |

| 1      | 0      | 1      | 0      | 1       |

| 1      | 0      | 1      | 1      | 0       |

| 1      | 1      | 0      | 0      | 0       |

| 1      | 1      | 0      | 1      | 0       |

| 1      | 1      | 1      | 0      | 1       |

| 1      | 1      | 1      | 1      | 1       |

Тема: исследование шифраторов и дешифраторов.

Цель: ознакомление с принципом работы шифраторов и дешифраторов, исследование влияния управляющих сигналов.

Шифраторы (кодеры) используются чаще всего для преобразования десятичных чисел в двоичный или двоично-десятичный код, например, в микрокалькуляторах, в которых нажатие десятичной клавиши соответствует генерации соответствующего двоичного кода. Поскольку возможно нажатие сразу нескольких клавиш, в шифраторах используется принцип приоритета старшего разряда, т.е. при нажатии клавиш 9, 5 и 2 на выходе шифратора будет генерироваться код 1001, соответствующий цифре 9.

Дешифратор - логическая комбинационная схема, которая имеет п информационных входов и 2n выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2n выходов.

#### Задание №1. Исследование шифратора

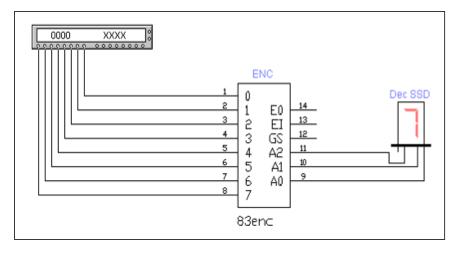

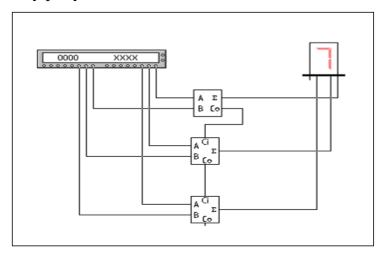

1. Соберите схему, показанную на рисунке 3.1

Рис. 3.1. Схема включения шифратора.

В ней используются следующие элементы:

- шифратор (ENC) Generic 8-to-3 Enc;

- генератор слов;

- дешифрующий семисегментный индикатор (Dec SSD).

При моделировании необходимо обратить внимание на реализацию принципа **приоритета**, при этом следует учесть, что все входы и выходы — инверсные (в программе EWB они ошибочно показаны прямыми).

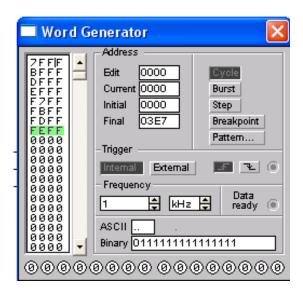

2. Сделайте двойной щелчок по генератору слов и занесите соответствующие коды в поле Binary в адреса с 0000 по 0007. Запустите модель в пошаговом режиме (кнопка Step). Генератор слов показан на Рис. 3.2.

Рис. 3.2. Генератор слов.

3. Занесите полученные на табло результаты в таблицу истинности.

Таблица 3.1. Таблица истинности

|   |   |   | Bxc | оды |   |   |   |       | Вых | оды |    |

|---|---|---|-----|-----|---|---|---|-------|-----|-----|----|

| 0 | 1 | 2 | 3   | 4   | 5 | 6 | 7 | Табло | A2  | A1  | A0 |

|   |   |   |     |     |   |   |   |       |     |     |    |

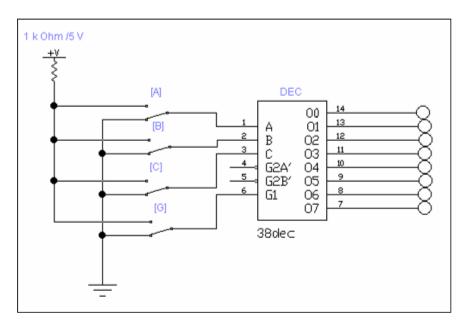

# Задание №2. Исследование дешифратора

1) Соберите схему, показанную на рисунке 3.3

Рис. 3.3. Схема включение дешифратора.

В ней используются следующие элементы:

- дешифратор (DEC) Generic 3-to-8 Dec;

- 8 пробников логического уровня;

- источник сигнала «логическая единица»; заземление;

- соединяющих узлов;

- 4 ключа, управляемые клавишей (кнопка Switch на панели Basic).

Ключи могут быть замкнуты или разомкнуты при помощи управляющих клавиш на клавиатуре. Имя управляющей клавиши можно ввести с клавиатуры в диалоговом окне, появляющемся после двойного щелчка мышью на изображении ключа.

2) Занесите полученные результаты моделирования в таблицу истинности. Выясните, для чего нужен вход G1.

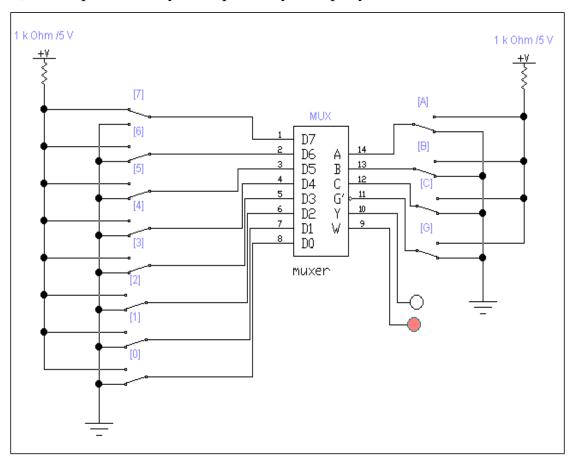

Тем: исследование мультиплексоров и сумматоров.

**Цель:** ознакомление с принципом работы мультиплексоров и сумматоров.

Мультиплексор - комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней информационных управления. Кроме И управляющих входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение независимо от значений информационных и управляющих сигналов.

Арифметические сумматоры составной являются частью так называемых арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти. В программе EWB арифметические сумматоры представлены в библиотеке Digital двумя устройствами, базовыми показанными: полусумматором И полным сумматором. Они имеют следующие назначения выводов: А, В — входы слагаемых,  $\Sigma$  — результат суммирования. Со — выход переноса, Сі — вход переноса. Многоразрядный сумматор создается на базе одного полусумматора и несколько полных сумматоров.

# Задание №1

1) Постройте схему, изображённую на рисунке 4.1

Рис. 4.1. Схема включения мультиплексора.

В ней используются следующие элементы:

- мультиплексор (MUX) Generic 1-of-8 Mux;

- 2 пробника логического уровня;

- 2 источника сигнала «логическая единица»; 2 заземления;

- 20 соединяющих узлов;

- 12 ключей, управляемых клавишей (кнопка Switch на панели Basic).

# Обозначения:

- D0-D7 информационные входы;

- А, В и С адресные входы;

- G вход разрешения

- Y и W выходы,

- 2) Включите схему. С помощью ключа G установите на входе G

Поочередно мультиплексора уровень логического нуля. подавая все возможные комбинации логических уровней при помощи ключей А, В, С на соответствующие входы мультиплексора, ДЛЯ каждой комбинации помощью логических пробников определите, переключение какого из ключей левой состояние мультиплексора. части схемы изменяет выходов Обозначение соответствующего входа мультиплексора запишите в таблицу, указав при этом, как передается входной сигнал на выходы мультиплексора (напрямую или с инверсией). Например, если переключение изменяет состояние выходов мультиплексора, В таблице в строке с соответствующей комбинацией уровней сигналов на входах А, В, С следует записать для выхода Y – D

| Α | В | С | Y | W |

|---|---|---|---|---|

| 0 | 0 | 0 |   |   |

| 0 | 0 | 1 |   |   |

| 0 | 1 | 0 |   |   |

| 0 | 1 | 1 |   |   |

| 1 | 0 | 0 |   |   |

| 1 | 0 | 1 |   |   |

| 1 | 1 | 0 |   |   |

| 1 | 1 | 1 |   |   |

Таблица 3.1. Таблица истинности.

3) Установите при помощи ключа G уровень логической единицы на входе G микросхемы. Запишите обозначения выводов, которые при переключении соответствующих ключей в левой части схемы не влияют на состояние выходов микросхемы.

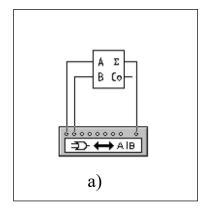

Задание №2. Исследование полусумматора.

1) Собрать схему рисунка 4.2.а)

Рис. 4.2. Схемы подключения сумматоров

- 2) После подключения полусумматора к преобразователю согласно рис. 4.2.а). Двойным щелчком по анализатору открываем диалоговое окно и последовательно нажимаем кнопки: → → 1011 , 1011 → AlB , в результате получаем таблицу истинности и булево выражение. Определяем, функцию какого элемента он выполняет?

- 3) Изменяем схему, подключив клемму ОUТ анализатор к выходу Со полусумматора выполняем действия аналогичные в п.2. Определяем, функцию какого элемента он выполняет?

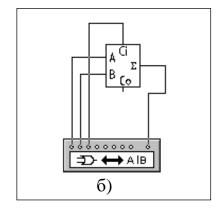

## Задание №3. Исследование полного сумматора.

- 1) Собрать схему рисунка 4.2.б)

- 2) После подключения сумматора к преобразователю согласно рис. 4.2.б). Двойным щелчком по анализатору открываем диалоговое окно и последовательно нажимаем кнопки: → → 1011 , 1011 → AlB , в результате получаем таблицу истинности и булево выражение. Определяем, функцию какого элемента он выполняет?

- 3) Изменяем схему, подключив клемму ОUТ анализатор к выходу Со сумматора выполняем действия аналогичные в п.2. Определяем, функцию какого элемента он выполняет?

# Задание №4. Исследование трехразряного сумматора

1) Собрать схему рисунка 4.3.

Рис. 4.3. Схема трехразрядного сумматора

#### Схема состоит из:

- 2-х полных сумматоров;

- полусумматора;

- генератора слов;

- дешифрующего семисегментного индикатора (Dec SSD).

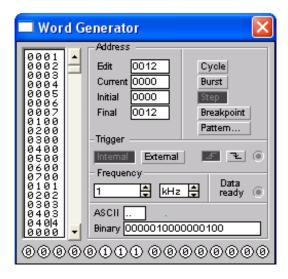

- 6.3. Сделайте двойной щелчок по генератору слов и занесите соответствующие коды в левое поле в адреса с 0000 по 0012. Запустите модель в пошаговом режиме (кнопка Step). Генератор слов показан на рис. 4.4. Занесите полученные на табло результаты в таблицу истинности.

Рис. 4.4. Генератор кода

Тема: исследование цифровых компараторов и устройств чётности.

Цель: ознакомление с принципом работы компаратора и устройств чётности.

Цифровые компараторы (от английского compare — сравнивать) выполняют сравнение двух чисел A, B одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство A=B или неравенства A<B, A>B. Результат сравнения отображается в виде логического сигнала на одноименных выходах.

Операция контроля четности двоичных чисел позволяет повысить надежность передачи и обработки информации. Ее сущность заключается в суммировании по модулю 2 всех разрядов с целью выяснения четности числа, что позволяет выявить наиболее вероятную ошибку в одном из разрядов двоичной последовательности.

Обнаружение ошибок путем введения дополнительного бита четности происходит следующим образом. На передающей стороне передаваемый код анализируется и дополняется контрольным битом до четного или нечетного числа единиц в суммарном коде. Соответственно суммарный код называется четным или нечетным. В случае нечетного кода дополнительный бит формируется таким образом, чтобы сумма всех единиц в передаваемом коде, включая контрольный бит, была нечетной. При контроле четности все, естественно, наоборот.

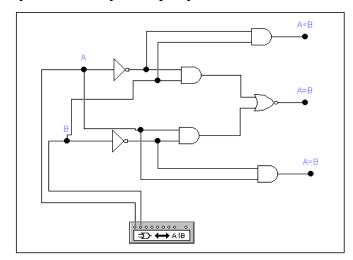

# Задание №1. Исследование цифрового компаратора

1) Собрать схему, показанную на рисунке 5.1

Рис. 5.1. Схема одноразрядного цифрового компаратора.

Компаратор состоит из двух элементов НЕ, четырех элементов И и одного элемента ИЛИ-НЕ.

Для исследования компаратора к нему подключен логический преобразователь.

Подсоединяя клемму логического преобразователя OUT к каждому выходу компаратора, получить таблицу истинности и булево выражение для каждого режима работы компаратора.

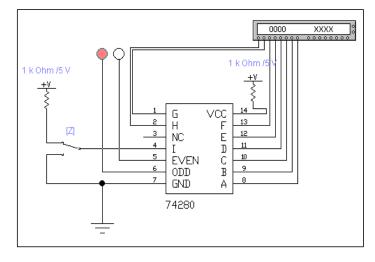

# Задание №2. Исследование устройства четности

1) Занесите схему, показанную на рис. 5.2

Рис.5.2. Схема включения ИМС 74280

ИМС 74280 имеет 9 входов (A, B...I) и два выхода (EVEN, ODD), один из которых — инверсный. Вход I используется для управления видом контроля (0 — контроль четности, 1 — контроль нечетности) и управляется переключателем Z (управляется с клавиатуры одноименной клавишей). Вывод NC — not connection — пустой, т.е. внутри ИМС к нему ничего не подключено.

2) Проверить правильность функционирования схемы с помощью генератора слова, при этом тип контроля (четности или нечетности) выбирается переключателем Z; на входы рассматриваемого устройства подаются различные двоичные комбинации; состояние выходов ИМС контролируется подключенными к ним светоиндикаторами (логическими пробниками). Результаты занести в таблицу (минимум 4 значения):

Таблица 5.1. Таблица истинности

| Входы   | Выходы |     |     |

|---------|--------|-----|-----|

| Кодовое | Z      | EVE | ODD |

|         |        |     |     |

Тема: исследование триггеров.

Цель: ознакомление с принципом работы триггеров.

Для проведения исследования триггерных схем уже нельзя использовать логический преобразователь, поскольку триггер является элементом памяти.

# Задание №1. Получение таблиц истинности триггеров

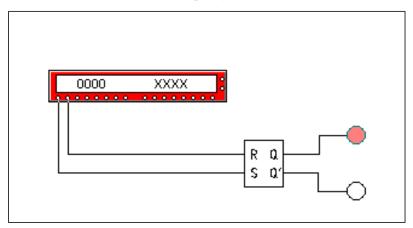

1) Создайте схему, показанную на рисунке 6.1.

Рис. 6.1. Схема для исследования RS-триггера

В схеме к входам триггера подключен генератор слова и светодиодные индикаторы к выходам.

2) Получить таблицу истинности триггера, подавая на входы различные комбинации (минимум их 6). Двойным щелчком по генератору слов открыть диалоговое окно и занести необходимые слова. Установите адрес начала (Initial) в **0000** и адрес конца (Final) в 0005(для 6 вариантов) Работать с генератором слов нужно в пошаговом режиме (кнопка **STEP**). Результаты занести в таблицу:

| № п/п | Входы |   | Выходы |    |  |

|-------|-------|---|--------|----|--|

|       | R     | S | Q      | Q' |  |

|       |       |   |        |    |  |

# Задание №2. Построение диаграмм

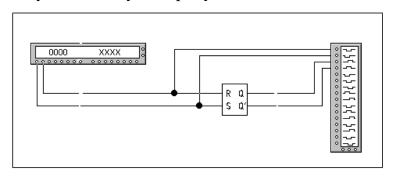

1) Собрать схему, показанную на рисунке 6.2.

Рис. 6.2. Схема включения RS-триггера

В схеме используется генератор слов (Word Generator) и логический анализатор (Logig Analyzer)

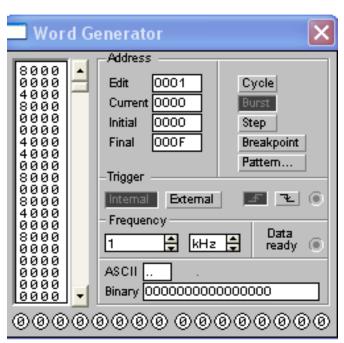

2) Двойным щелчком по генератору слов откройте диалоговое окно и задайте 16 слов, как показано на рис. 6.3. Установите адрес начала (Initial) в **0000**, а адрес конца (Final) в **000F**. Щелкните по кнопке **Burst**, что подаст на входы триггера последовательно все 16 слов.

Рис. 6.3. Диалоговое окно генератора слов

3) Откройте двойным щелчком логический анализатор. Убедитесь в правильности получения результатов.

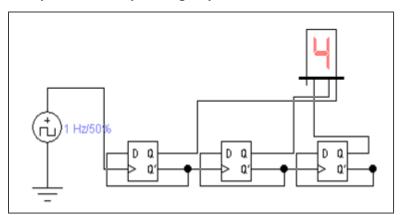

Тема: исследование счётчиков.

Цель: ознакомление с принципом работы счётчика.

Счетчик - устройство для подсчета числа входных импульсов. Число, представляемое состоянием его выходов по фронту каждого входного импульса, изменяется на единицу. Счетчик можно реализовать на нескольких триггерах. В суммирующих счетчиках каждый входной импульс увеличивает число на его выходе на единицу, в вычитающих счетчиках каждый входной импульс уменьшает это число на единицу.

### Задание №1 Исследование счетчиков

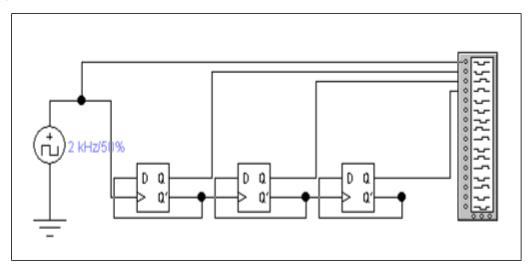

1) Собрать схему, показанную на рисунке 7.1.

Рис. 7.1. Схема трёхразрядного суммирующего счётчика

- 2) Дважды щёлкните по источнику импульсов и установите частоту 1 Гц, закройте диалоговое окно.

- 3) Понаблюдайте за изменением индикатора.

- 4) Выключите схему и отредактируйте её, чтобы получить вычитающий счётчик.

Вычитающий счётчик можно получить двумя способами:

а) Считывать выходные сигналы счетчика не с прямых, а с инверсных выходов триггеров;

- б) Изменить структуру связей в счетчике: подавать на счетный вход следующего триггера сигнал не с инверсного, а с прямого выхода предыдущего.

- 5) Подсоедините вместо семи сегментного индикатора логический анализатор, как показано на рисунке 7.2.

- 6) Дважды щёлкните по источнику импульсов и установите частоту 2 КГц.

- 7) Двойным щелчком по анализатору откройте диаграммы и запустите схему. Через несколько секунд остановите работу схемы.

- 8) Зарисуйте и проанализируйте диаграммы суммирующего и вычитающего счётчиков.

Рис. 7.2. Схема счетчика для анализа диаграмм

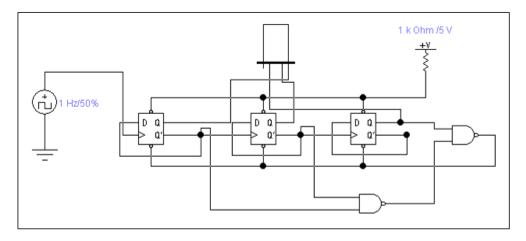

# Задание №2. Изучение работы делителя частоты

Счетчик должен иметь 5 состояний, которые в простейшем случае образуют последовательность: {O, 1, 2, 3, 4}. Циклическое повторение этой последовательности означает, что коэффициент деления счетчика равен 5. Схема такого счётчика изображена на рисунке 7.3

Рис. 7.3. Схема счётчика с коэффициентом деления 5

- 1) Нарисуйте схему рисунка 7.3.

- 2) Сделайте двойной щелчок на источнике импульсов и установите частоту 1 Гц.

- 3) Включите схему и понаблюдайте за индикатором.

Тема: исследование регистров.

Цель: ознакомление с принципом работы регистра.

преобразование Основное назначение регистров хранение многоразрядных двоичных чисел. Выдача информации к внешним устройствам характеризует операцию вывода или считывания. Запись информации в регистр не требует его предварительного обнуления. Все регистры в зависимости от функциональных свойств подразделяются на две категории накопительные (регистры памяти, хранения) и сдвигающие. В свою очередь, сдвигающие регистры делятся по способу ввода и вывода информации на комбинированные параллельные, последовательные (параллельно-И последовательные последовательно-параллельные), И направлению передачи (сдвига) информации — на однонаправленные и реверсивные.

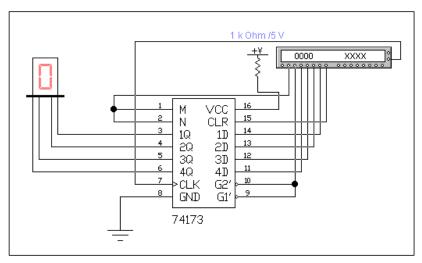

# Задание №1. Исследование регистра хранения

1) Нарисовать схему, изображённую на рисунке 8.1.

Рис. 8.1. Схема включения регистра 74173

К155ИР15 — четырехразрядный регистр. Он имеет выходы 1Q...4Q с третьим Z-состоянием (при сигнале 1 на выводах G2, G1), а его входы 1D...4D

снабжены логическими элементами разрешения записи путем подачи логического 0 на входы M, N (в EWB ошибочно показаны прямыми). Используется регистр как четырехразрядный источник кода, способный обслуживать непосредственно шину данных цифровой системы.

- 2) Дважды щёлкните по генератору слов и занесите в него информацию с адреса **0000** по **0009**, показанную в таблице 8.1

- 3) Запустите схему в пошаговом режиме (кнопка Step) и запишите показания индикатора в таблицу 8.1.

- 4) Проанализируйте полученные данные.

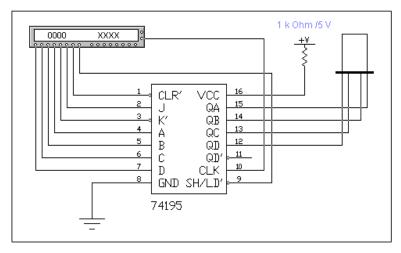

# Задание №2. Исследование регистров сдвига

- 1) Нарисовать схему, показанную на рисунке 8.2.

- 2) Дважды щёлкните по генератору слов и занесите в него информацию с адреса **0000** по **0015**, показанную в таблице 8.2

- 1 сдвиг и установка по первому каскаду (JK=11);

- 2 сдвиг и сброс по первому каскаду (ЈК=00);

- 3 сдвиг и переключение первого каскада (JK=10); 4 сдвиг и хранение в первом каскаде (JK=01).

- 3) Запустите схему в пошаговом режиме (кнопка Step) и запишите показания индикатора в таблицу 8.2.

- 4) Проанализируйте полученные данные.

Рис. 8.2. Схема включения регистра 74195 в режиме сдвига

Если на входе LD/SH присутствует напряжение низкого (активного) уровня, все четыре триггера регистра запускаются одним тактовым перепадом (от низкого уровня к высокому). Тогда данные от параллельных входов А...D передаются на соответствующие выходы QA...QD.

Для режима сдвига напряжение на входе LD/SH надо зафиксировать на высоком уровне. Низким уровнем на входе CLR всем выходным сигналам присваивается низкий уровень.

Таблица 8.1. Результаты эксперимента

| No |         | Выход     |    |    |    |    |     |  |

|----|---------|-----------|----|----|----|----|-----|--|

|    | M,<br>N | G1,<br>G2 | 4D | 3D | 2D | 1D | CLR |  |

| 1  | 0       | 0         | 0  | 0  | 0  | 1  | 0   |  |

| 2  | 0       | 0         | 0  | 0  | 1  | 0  | 0   |  |

| 3  | 0       | 0         | 0  | 1  | 0  | 0  | 0   |  |

| 4  | 0       | 0         | 1  | 0  | 0  | 0  | 0   |  |

| 5  | 0       | 0         | 1  | 1  | 1  | 1  | 0   |  |

| 6  | 0       | 1         | 1  | 0  | 0  | 0  | 0   |  |

| 7  | 0       | 0         | 1  | 0  | 0  | 1  | 0   |  |

| 8  | 0       | 0         | 1  | 1  | 1  | 1  | 1   |  |

| 9  | 1       | 0         | 1  | 0  | 0  | 1  | 0   |  |

| 10 | 0       | 0         | 1  | 0  | 1  | 1  | 0   |  |

Таблица 8.2. Результаты эксперимента

| №  | Входы |   |   |   |   |   |     |       |   |

|----|-------|---|---|---|---|---|-----|-------|---|

|    | D     | С | В | A | K | J | CLR | SH/LD | _ |

| 1  | 0     | 0 | 0 | 1 | 0 | 0 | 1   | 0     |   |

| 2  | 0     | 0 | 0 | 0 | 0 | 0 | 1   | 1     |   |

|    |       |   |   |   |   |   |     |       |   |

| 3  | 0     | 0 | 0 | 0 | 0 | 0 | 1   | 1     |   |

| 4  | 0     | 0 | 0 | 0 | 0 | 0 | 1   | 1     |   |

| 5  | 0     | 0 | 0 | 1 | 1 | 1 | 1   | 0     |   |

| 6  | 0     | 0 | 0 | 0 | 1 | 1 | 1   | 1     |   |

| 7  | 0     | 0 | 0 | 0 | 1 | 1 | 1   | 1     |   |

| 8  | 0     | 0 | 0 | 0 | 1 | 1 | 1   | 1     |   |

| 9  | 0     | 0 | 0 | 0 | 1 | 1 | 1   | 1     |   |

| 10 | 0     | 0 | 0 | 0 | 1 | 1 | 1   | 1     |   |

| 11 | 0     | 0 | 0 | 1 | 0 | 1 | 1   | 0     |   |

| 12 | 0     | 0 | 0 | 0 | 0 | 1 | 1   | 1     |   |

| 13 | 0     | 0 | 0 | 0 | 0 | 1 | 1   | 1     |   |

| 14 | 0     | 0 | 0 | 0 | 0 | 1 | 1   | 1     |   |

| 15 | 0     | 0 | 0 | 0 | 0 | 1 | 1   | 1     |   |

| 16 | 0     | 0 | 0 | 0 | 0 | 1 | 1   | 1     |   |

| 17 | 0     | 0 | 0 | 1 | 1 | 0 | 1   | 0     |   |

| 18 | 0     | 0 | 0 | 0 | 1 | 0 | 1   | 1     |   |

| 19 | 0     | 0 | 0 | 0 | 1 | 0 | 1   | 1     |   |

| 20 | 0     | 0 | 0 | 0 | 1 | 0 | 1   | 1     |   |

| 21 | 0     | 0 | 0 | 0 | 1 | 0 | 1   | 1     |   |

| 22 | 0     | 0 | 0 | 0 | 1 | 0 | 1   | 1     |   |

Тема: арифметико-логическое устройство.

Цель: ознакомление с принципом работы АЛУ

## Задание №1

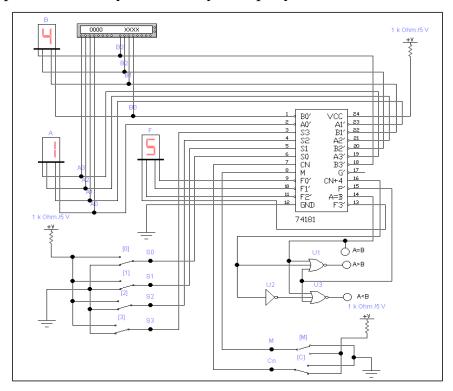

1) Нарисовать схему, показанную на рисунке 9.1.

Рис. 9.1. АЛУ на ИМС 74181

Если M=1 – выполняются логические операции, если M=0 – арифметические операции.

При выполнении арифметических операций, если Cn=1 — выполняются операции без учёта переноса, если же Cn=0 — с учётом переноса.

- 2) Занести в генератор слов операнды A и В. Генератор слов должен работать в пошаговом режиме (кнопка **Step** должна быть нажата).

- 3) Запустить схему, результат занести в таблицу.

- 4) Изменить комбинацию сигналов на входе, согласнотаблице, остановить схему, а затем снова её запустить и занести результат в таблицу.

- 5) Повторять выполнение пункта 4, пока все таблицы не будут заполнены.

Таблица 9.1. Для М=0

| No | <b>S</b> 3 | S2 | <b>S</b> 1 | S0 | Операция  | A | В | I    | Ę    |

|----|------------|----|------------|----|-----------|---|---|------|------|

|    |            |    |            |    | •         |   |   | Cn=1 | Cn=0 |

| 1  | 0          | 0  | 0          | 0  | A         |   |   |      |      |

| 2  | 0          | 0  | 0          | 1  | A+B       |   |   |      |      |

| 3  | 0          | 0  | 1          | 0  | A+B'      |   |   |      |      |

| 4  | 0          | 0  | 1          | 1  | -1        |   |   |      |      |

| 5  | 0          | 1  | 0          | 0  | A+AB'     |   |   |      |      |

| 6  | 0          | 1  | 0          | 1  | (A+B)+AB' |   |   |      |      |

| 7  | 0          | 1  | 1          | 0  | A-B-1     |   |   |      |      |

| 8  | 0          | 1  | 1          | 1  | AB'-1     |   |   |      |      |

| 9  | 1          | 0  | 0          | 0  | A+AB      |   |   |      |      |

| 10 | 1          | 0  | 0          | 1  | A+B       |   |   |      |      |

| 11 | 1          | 0  | 1          | 0  | (A+B')+AB |   |   |      |      |

| 12 | 1          | 0  | 1          | 1  | AB-1      |   |   |      |      |

| 13 | 1          | 1  | 0          | 0  | A+A       |   |   |      |      |

| 14 | 1          | 1  | 0          | 1  | (A+B)+A   |   |   |      |      |

| 15 | 1          | 1  | 1          | 0  | (A+B')+A  |   |   |      |      |

| 16 | 1          | 1  | 1          | 1  | A-1       |   |   |      |      |

В таблице — «В'» обозначается инверсия В. Правильность выходов A=B, A>B, A<B проверить в п. 7.

Таблица 9.2. Для М=1

| №  | <b>S</b> 3 | S2 | <b>S</b> 1 | S0 | Операция | A | В | F |

|----|------------|----|------------|----|----------|---|---|---|

| 1  | 0          | 0  | 0          | 0  | A'       |   |   |   |

| 2  | 0          | 0  | 0          | 1  | (A+B)'   |   |   |   |

| 3  | 0          | 0  | 1          | 0  | A'+B     |   |   |   |

| 4  | 0          | 0  | 1          | 1  | 0        |   |   |   |

| 5  | 0          | 1  | 0          | 0  | (A+B)'   |   |   |   |

| 6  | 0          | 1  | 0          | 1  | B'       |   |   |   |

| 7  | 0          | 1  | 1          | 0  | A B      |   |   |   |

| 8  | 0          | 1  | 1          | 1  | A+B'     |   |   |   |

| 9  | 1          | 0  | 0          | 0  | A'* B    |   |   |   |

| 10 | 1          | 0  | 0          | 1  | (A*B)'   |   |   |   |

| 11 | 1          | 0  | 1          | 0  | В        |   |   |   |

| 12 | 1          | 0  | 1          | 1  | A+B      |   |   |   |

| 13 | 1          | 1  | 0          | 0  | 1        |   |   |   |

| 14 | 1          | 1  | 0          | 1  | A*B'     |   |   |   |

| 15 | 1          | 1  | 1          | 0  | A*B      |   |   |   |

| 16 | 1          | 1  | 1          | 1  | A        |   |   |   |

Значения А и В спросить у преподавателя.

*Тема: оперативные запоминающие устройства, постоянные запоминающие устройства.*

Цель: моделирование процесса программирования ПЗУ с пережигаемыми перемычками. Ознакомление с принципом работы ОЗУ. Моделирование процесса программирования ПЗУ с пережигаемыми перемычками.

### Задание №1. Исследование оперативного запоминающего устройства

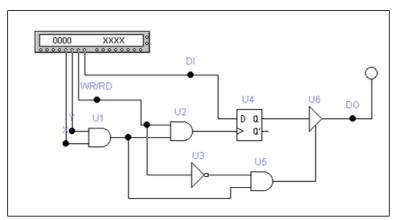

1) Нарисовать схему, показанную на рисунке 10.1.

Рис. 10.1. Схема ячейки памяти

При записи в ячейку памяти (см. рис. 10.1) на соответствующей разрядной шине устанавливается 1 или 0, на входе WR/RD' устанавливается сигнал 1 и после стробирования счетчика или дешифраторов адреса сигналом СS (на адресных входах X и Y сигнал 1) срабатывают элементы U1, U2. Положительный перепад сигнала с элемента U2 поступает на тактовый вход D-триггера U4, в результате чего в нем записывается 1 или 0 в зависимости от уровня сигнала на его D-входе.

При чтении из ячейки памяти на входе WR/RD устанавливается 0, при этом срабатывают элементы U1, U3, U5 и на вход РАЗРЕШЕНИЕ ВЫХОДА буферного элемента U6 поступает разрешающий сигнал, в результате чего сигнал с Q-выхода D-триггера передается на разрядную шину DO. Для проверки функционирования ячейки памяти используется генератор слова.

- 2) Занести в генератор слова комбинации из таблицы 10.1.

- 3) Заполнить таблицу 10.1 и определить: какая операция выполняется при каждой комбинации чтение 1 (0) или запись 1 (0)?

Таблица 10.1 Результат эксперимента

|  | W |  | Режим |

|--|---|--|-------|

|  | 1 |  |       |

|  | 0 |  |       |

|  | 1 |  |       |

|  | 0 |  |       |

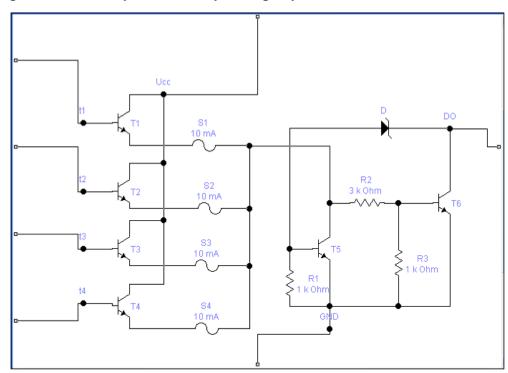

## Задание №2.

1) Нарисовать схему, показанную на рисунке 10.2.

Рис. 10.2 Внутренняя структура ячейки памяти.

- 2) Выделить все элементы схемы и выполнить команду Create Subcircuit, в появившемся диалоговом окне задать имя pzu\_in1 и щёлкнуть по кнопке Replace in Circuit.

- 3) На экране вместо выделенного фрагмента появится элемент с заданным именем. Двойным щелчком откройте схему и дорисуйте линии символизирующие входы и выходы. Затем закройте схему.

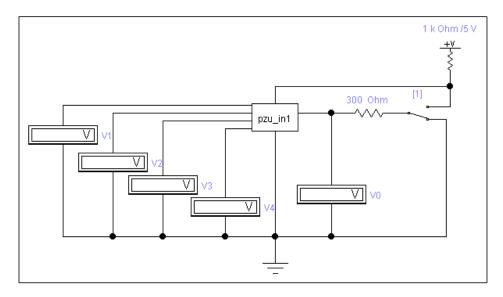

- 4) Нарисуйте схему, показанную на рисунке 10.3.

Рис. 10.3. Модель ПЗУ с дополнительными элементами.

Задайте значения нагрузок для V0, V1, V2, V3 и V4 соответственно: 10 кОм, 5000 МОм, 6000 МОм, 100 кОм, 3000 МОм.

- 5) Включите схему, переведите ключ на источник 5 В. При этом начнут изменяться показания индикаторов на вольтметрах.

- 6) Выключите схему, двойным щелчком откройте pzu\_in1.

- 7) Затем снова включите схему и посмотрите, что произошло с перемычкой S3.

- 8) Смоделируйте пережигание перемычки S4.

# Список литературы

- 1. <a href="http://www.planetaknig.com">http://www.planetaknig.com</a>

- 2. Волович Г.И. Схемотехника аналоговых и аналого-цифровых электронных устройств. 2-е изд., испр. М.: Издательский дом «Додэка-XXI», 2007.-528c.

- 3. Максимов Н.В., Партыка Т.Л., Попов И.И. Архитектура ЭВМ и вычислительных систем: Учебник. М.: ФОРУМ: ИНФРА-М, 2006.

- 4. Микропроцессорные устройства автоматики: Учеб. пособие для вузов / А.А. Сазонов, А.Ю. Лукичев, В.Т. Николаев и др.; Под ред. А.А. Сазонова. М.: Энергоиздат, 1991.

- 5. Новожилов О.П. Основы цифровой техники / Учебное пособие.- М.: ИП РадиоСофт, 2004. 528c.

- 6. Расчёт элементов цифровых устройств / Л.Н.Преснухин, Н.В.Воробьёв, А.А.Шишкевич. 2-е изд., под ред.Л.Н.Преснухина. М.: «Высшая школа», 1991. 528с.

- 7. Схемотехника электронных систем. Цифровые устройства/ В.И.Бойко, А.Н.Гуржий, В.Я.Жуйков, А.А.Зори, В.М.Спивак, В.В.Багрий.- СПб.: БХВ-Петербург, 2004. -512с.

- 8. Угрюмов Е.П., Цифровая схемотехника: Учебное пособие для вузов. 2-е изд., перераб. и доп. СПб.: БХВ-Петербург, 2007. 800с.

- 9. Угрюмов Е.П. Цифровая схемотехника. СПб.: БХВ-Петербург, 2001. 528с.